geht er maskiert und nennt sich Gerechtigkeit

- Arthur Schnitzler

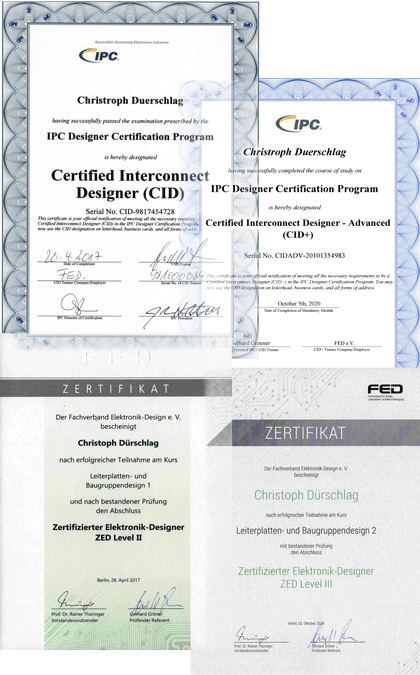

FED Fachverband für Design, Leiterplatten- und Elektronikfertigung:

Weiterbildung zum CID / CID+ (Certified Interconnect Designer)

Der Fachverband Elektronik Design (FED) ist in Internationalen Gremien mit der Ausarbeitung und Übersetzung von Richtlinien und Normen befasst.

Die Weiterbildung von Facharbeitern im Elektronik- Design und Produktionsbereich ist ein weiterer Wirkungsbereich.

In Zusammenwirken mit dem IPC hat der FED eine Qualifizierung für Leiterplattendesigner erarbeitet.

Aufbauend auf den IPC Abschluss zum "Certified Interconnect Designer" entwickelte der FED mittlerweile ein vierstufiges eigenes Kurssystem.

Auf Basis der international anerkannten IPC-Richtlinien bietet der FED in seinen Kursen eine eigene Prüfung zum ZED Zertifizierter Elektronik-Designer, ZED Level I - IV, sowie die vom IPC zertifizierte CID Prüfung optional an.

In den einzelnen Kurs Blöcken werden die Grundlagen des Leiterplattendesigns vermittelt.

In aufbauenden Kursen werden die Kentnisse zum PCB-Design Spezialisten vermittelt.

Die zwei redundanten CID und ZED Prüfungen, aber auch eine abschweifend chiffrierte Prüfungsvorbereitung beanspruchen wertvolle Kurszeit.

Der notwendige Zeitraum für Lerninhalte wird dadurch unnötig beschnitten.

Wenn es um die reine Wissenserweiterung geht empfehle ich die Kurse der Leiterplattenakademie.

Die CID & ZED Prüfung bleibt als anerkannter Abschluss im Lebenslauf erstrebenswert.

Die folgenden Schwerpunkte werden in der IPC CID / CID+ Schulung behandelt:

- DIN-Normen und IPC-Richtlinien

- Fertigungstechnologie Baugruppenfertigung

- Fertigungstechnologie LP-Herstellung

- Zusammenführung der Designgrundlagen

- Handlungsschema im PCB Produktprozess

- Komplexe Bauteile, Fine-Pitch & HDI

- Aufbau und Bearbeiten der Bauteile-Bibliothek

- Designregeln für die PCB Layout Erstellung

- Signalintegrität, Impedanzanpassung, EMV

- Notwendige Dokumente und Fertigungsunterlagen

Die Leiterplattenakademie in Berlin:

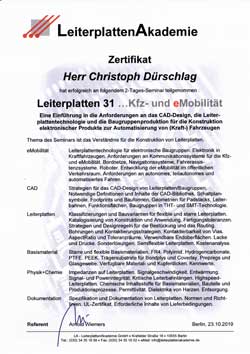

Tagesseminar: Leiterplatten 31 - Kfz- und eMobilität

Kfz- und eMobilität sind hier nur der Teaser.

Eingegangen wird auf die vielfältigen Anforderungen an das CAD-Design, die Leiterplattentechnologie und Baugruppenproduktion.

Ziel ist die Erweiterung des Wissens für die erfolgreiche Konstruktion elektronischer Produkte zur Automatisierung.

Die Abhängigkeiten zwischen den Disziplinen CAD, Leiterplatte und Baugruppenfertigung werden dargestellt.

Konstruktionsregeln, Fertigungstoleranzen, Produktionsvorgaben und deren Definition in der CAD-Bibliothek werden dargestellt.

Eigenschaften von Leiterbildern für die funktionale Integrität elektronischer Baugruppen. Stabilität, Entwärmung und die physikalische Qualität werden erörtert.

Ein sehr umfangreiches Paket für zwei Seminartage.

Fundierte Grundkenntnisse sollten daher bereits vorhanden sein.

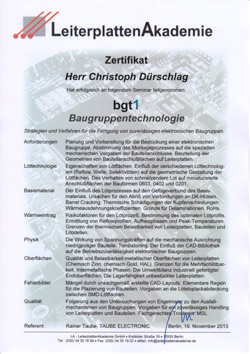

Tagesseminar: Baugruppentechnologie

Im Seminar Baugruppentechnologie, der Leiterplattenakademie Berlin berichtet der erfahrene Praktiker Rainer Taube aus seiner Praxis.

Er vermittelt anhand von Beispielen verständlich die Anforderungen aus der Produktion von Baugruppen an das PCB Design.

Es wurden Methoden und Kenntnisse für eine problemlose Bestückung der Leiterplatten aufgezeigt, in der die Leiterplattentechnologie, die Bauteil-Geometrien und die Montagetechniken optimal zusammenpassen.

Dieser Kurs ist meine persönliche Empfehlung!

Die folgenden Schwerpunkte wurden behandelt:

- Planung und Vorbereitung für die Baugruppenbestückung

- Eigenschaften von Lötflächen

- Oberflächen von Leiterplatten

- Basismaterial

- Wärmebeständigkeit

- Wärmeprofile für das Löten

- Physik des Lötens

- Fehlerbilder

- Delaminationen

- Qualitätsanforderungen

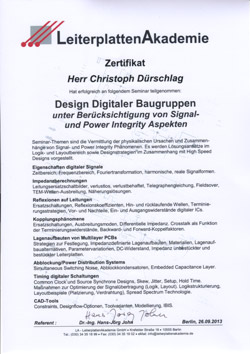

Tagesseminar: Design Digitaler Baugruppen

Im Seminar Design Digitaler Baugruppen, der Leiterplattenakademie Berlin wurden Methoden und Kenntnisse für eine zuverlässige Funktion und verbesserte EMV von Baugruppen aufgezeigt.

Vermittelt wurden die physikalischen Ursachen und Zusammenhänge von Signal- und Power-Integrity-Phänomenen.

Es wurden Lösungsansätze im Logik- und Layoutbereich sowie Designstrategien im Zusammenhang mit Digitalen-High-Speed-Designs vorgestellt.

Die folgenden Schwerpunkte wurden behandelt:

- Einflussgrößen auf die EMV

- Zeitparameter digitaler Signale

- Reale Signalformen

- Leitungen auf dem PCB

- Ersatzschaltbild einer Leitung

- Wellenwiderstand

- Reflexionen und Terminierungsstrategien

- Crosstalk

- Differenzielle Impedanz

- Definition von Lagenaufbauten

- Abblockkondensatoren

- Source synchrones Design

Tagesseminar: CAD1, Design von Leiterplatten

Im CAD1 Seminar der Leiterplattenakademie Berlin wird auf die Grundlagen des CAD-Designs von Leiterplatten vollumfänglich eingegangen.

Vermittelt werden umfassende Kenntnisse in der Fertigungstechnologie der Leiterplatte und auch In Bezug auf Baugruppen.

Die Zusammenhänge von CAM-Bearbeitung der LP-Hersteller der Entwicklung und Fertigung werden strukturiert beleuchtet.

Die Referentin Jennifer Vincenz ist viele Jahre im CAD-Design tätig mit einem breiten Wissensspektrum voll im Thema.

Die folgenden Schwerpunkte wurden behandelt:

- aktuelle Fertigungstechnologien

- Wärmekontrolle und Wärmeabfuhr

- Priorisierung bei der Platzierung

- und Produzierbarkeit µBGA, Flip Chip

- Einflussgrößen auf die Signalintegrität

- Crosstalk und Signalgeschwindigkeit

- Erfordernisse an die Bauteilbibliothek

- Grundlagen High-Speed-Design

- Fan-Out-Strategien

- Definition von Lagenaufbauten

- mechanischen Anforderungen

- Dokumentation und Postprozess

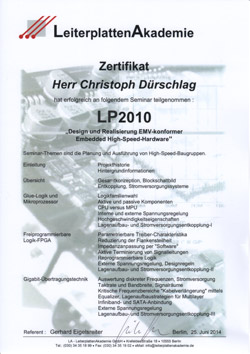

Tagesseminar: LP 2010

Der Begriff "Leiterplatte 2010" dürfte vielen Leiterplattendesignern bekannt sein.

In dieser Studie wurden in der Fachschrift Elektronik Praxis die Designanforderungen im gesamten Entwicklungsprozess: von der Bauteilauswahl, dem Leiterplattenaufbau zur physikalischen Ausführung der bestückten Baugruppe beschrieben.

Herr Eigelsreiter der vortragende dieses Seminars der Leiterplattenakademie Berlin hat das dort ausgezeichnete CPU-Board "meltemi" entwickelt.

An diesem Board zeigt Herr Eigelsreiter die notwendigen Voraussetzungen für Hochgeschwindigkeitsplattformen.

Die folgenden Schwerpunkte wurden behandelt:

- meltemi / Blockschaltbild

- Aufteilung der Funktionen eines Multilayer Designs

- Spezifikation von Bauteilen

- Stromversorgungssysteme

- Funktionsanalyse

- Interpretation von EMV Messergebnissen

- Signalintegrität

- Breitbandentkopplung

- LVDS-Routing

- Stromversorgungsflächen